PCB多层板叠层结构设计优化与制造工艺指南

2025-03-25 18:00:27

1280

以下是对PCB叠层结构设计的系统性优化整理,结合工程实践与制造工艺要求,以结构化形式呈现关键设计准则:

一、叠层架构优化设计

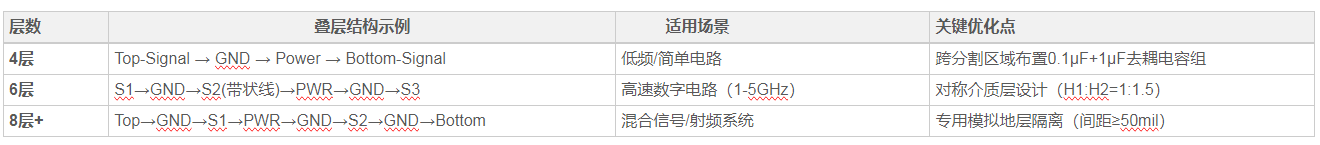

1. 层数选择与典型配置

设计原则

高速信号层优先布设于内层带状线(距参考平面≤4mil)

电源/地平面相邻布局,间距≤3mil以增强耦合电容(典型0.5nF/cm²)

敏感信号隔离:模拟/数字信号层间插入地平面,间距≥3倍介质厚度

二、对称性工程规范

1. 叠层对称设计

铜厚镜像对称

示例:Top(1oz)/L2/L3(3oz)/L4(3oz)/L5/L6(1oz) → 阶梯式铜厚平衡

厚铜层(≥2oz)相邻层采用补偿设计:每增加1oz铜厚,两侧各加1张PP

介质对称分布

6层板典型对称结构:Top(5mil)/Prepreg(4mil)/GND(1oz)/Core(40mil)/PWR(1oz)/Prepreg(4mil)/Bottom(5mil)

2. 铜密度均衡方案

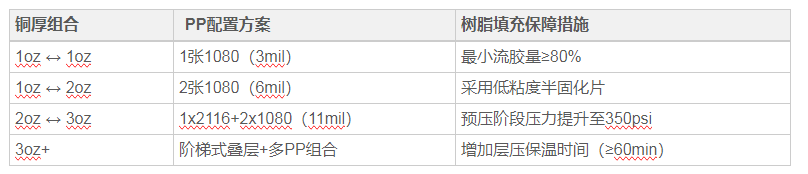

3. PP片选型策略

三、材料选型与工艺适配

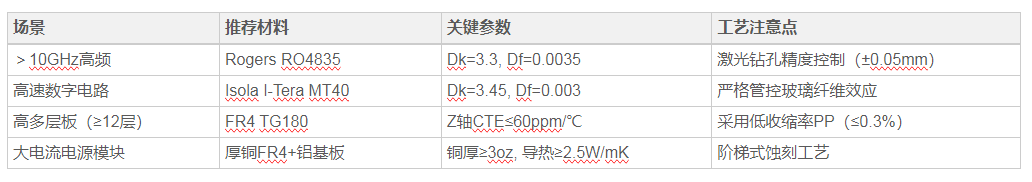

1. 基材选型对照表

2. 特殊工艺规范

混合材料叠层:Rogers与FR4混压时,对称位置使用相同热膨胀系数材料

厚铜板制造:3oz以上铜层采用差分蚀刻(先蚀刻至2oz,二次图形化至目标厚度)

高精度阻抗:采用UV激光直接成像(LDI)技术,线宽公差控制在±0.2mil

四、阻抗控制工程方法

1. 阻抗设计流程

预设计阶段

确定信号类型(单端/差分)及目标阻抗(50Ω/90Ω/100Ω)

选择参考平面组合(GND-GND或GND-PWR)

参数建模

带状线阻抗计算示例(SI9000模型)

H = 4.5 # 介质厚度(mil)

W = 5.2 # 线宽(mil)

T = 1.4 # 铜厚(mil)

Er = 4.2 # 介电常数

Z0 = 87/(sqrt(Er+1.41)) * ln(5.98H/(0.8W+T)) # 计算结果需匹配目标值±3%

制造补偿

侧蚀补偿:线宽增加ΔW=0.2×√(铜厚/1oz)

铜厚补偿:1oz按1.2mil计入模型

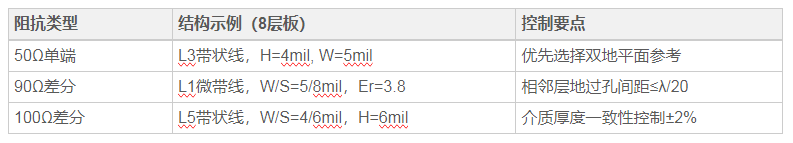

2. 典型阻抗结构参数