阻抗匹配与PCB设计技术要点

随着科技进步与集成电路的快速发展,电子信号传输频率和速率持续提升,对PCB导线的信号传输性能提出了更高要求。为确保输出端信号完整、准确地传输至接收器件输入端,阻抗匹配已成为PCB设计中的核心关键环节。

一、核心概念定义

阻抗(Electrical Impedance):电路中电阻、电感、电容对交流电的总阻碍作用,常用符号Z表示,单位为欧姆(Ω)。阻抗值并非固定不变,其大小由交流电频率、电阻(R)、电感(L)、电容(C)共同决定,且随频率变化而动态调整。

阻抗匹配(Impedance Matching):信号源或传输线与负载之间的适配设计方式,分为低频匹配和高频匹配两类,核心目的是减少信号反射、保障信号质量,具体差异如下:

应用场景 | 核心特点 | 反射处理原则 |

|---|---|---|

低频电路 | 信号波长远大于传输线长度,传输线可视为“短线” | 反射影响极小,可忽略不计 |

高频电路 | 信号波长与传输线长度可比拟,反射信号易叠加原信号 | 必须通过阻抗匹配消除/减少反射,避免信号畸变 |

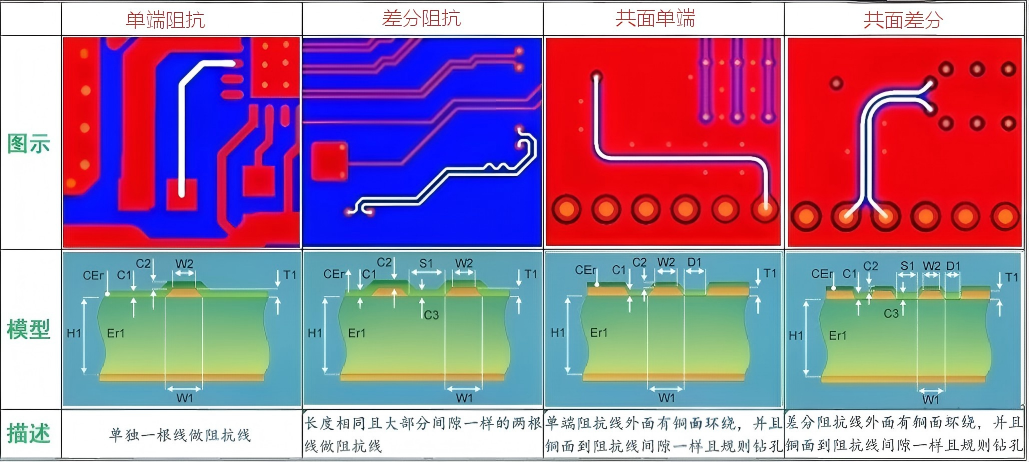

二、常规阻抗线类型(四种核心形式)

阻抗线类型 | 结构特点 | 典型应用场景 |

|---|---|---|

单端阻抗线 | 单根信号导线,以相邻地/电源层为参考 | SDIO(50Ω)、普通控制信号等 |

差分阻抗线 | 成对平行导线,通过信号差分传输抗干扰 | USB(90Ω)、HDMI、DDR等高速信号 |

共面阻抗线 | 信号导线两侧伴有参考铜皮,同层形成参考回路 | 高频信号场景,需强化电磁屏蔽时 |

微带线阻抗线 | 导线位于PCB表层,下方紧邻参考层(地/电源) | 外层高速信号,需兼顾信号完整性与工艺可行性 |

三、阻抗设计核心注意事项

(一)基础设计要求

阻抗线可设计于PCB外层(上述四种类型均为外层典型形式)或内层,需根据信号走向合理规划。

阻抗值需依据产品设计方案及芯片规格确定,元器件厂商通常会明确信号源与接收端的阻抗标准(示例:SDIO单端50Ω、USB差分90Ω)。

阻抗线必须配置阻抗参考层,优先以相邻的接地层或电源层作为参考层(示例:顶层阻抗线默认以第二层为参考层)。

参考层核心作用是为信号提供稳定回流路径,并实现电磁屏蔽,因此阻抗线对应的参考层区域必须采用实心铜皮完整覆盖,严禁开窗或铜皮断裂。

(二)阻抗值关键影响因素

影响因素 | 与阻抗值的关系 | 核心说明 |

|---|---|---|

线宽 | 反比 | 线宽越细,阻抗值越高;线宽越粗,阻抗值越低 |

介电常数 | 反比 | 介电常数越低,信号传输损耗越小,阻抗值越高 |

防焊厚度 | 反比 | 防焊厚度越厚,对信号的耦合影响越大,阻抗值越低 |

铜厚度(面铜) | 反比 | 铜厚越薄,信号传输电阻越大,阻抗值越高 |

线距(阻抗线间/与铜皮间距) | 正比 | 间距越大,信号间耦合干扰越小,阻抗值越高 |

介层厚度 | 正比 | 介层越厚,信号与参考层耦合越弱,阻抗值越高 |

(三)阻抗计算与基础术语说明

阻抗计算方法:可下载专业阻抗计算软件(如SI9000),结合我司层压参数精准计算。

核心术语界定:

线宽:单根阻抗线的两个边缘之间的直线距离(即导线粗细);

线隙:不同阻抗线边缘之间,或阻抗线边缘与铜皮边缘之间的距离。

四、阻抗管控下单说明

若PCB需进行阻抗管控,下单时必须满足以下要求:

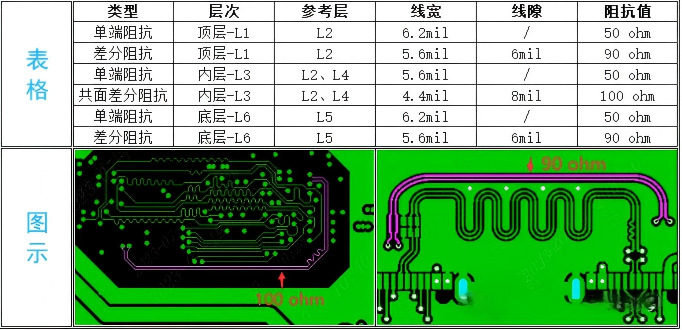

1. 需将阻抗要求(含阻抗值、对应线网、参考层等信息)以表格或图示形式清晰呈现;

2. 将上述阻抗要求文件与PCB设计文件一同压缩打包;

3. 确保文件完整性,避免因信息缺失导致阻抗管控偏差。