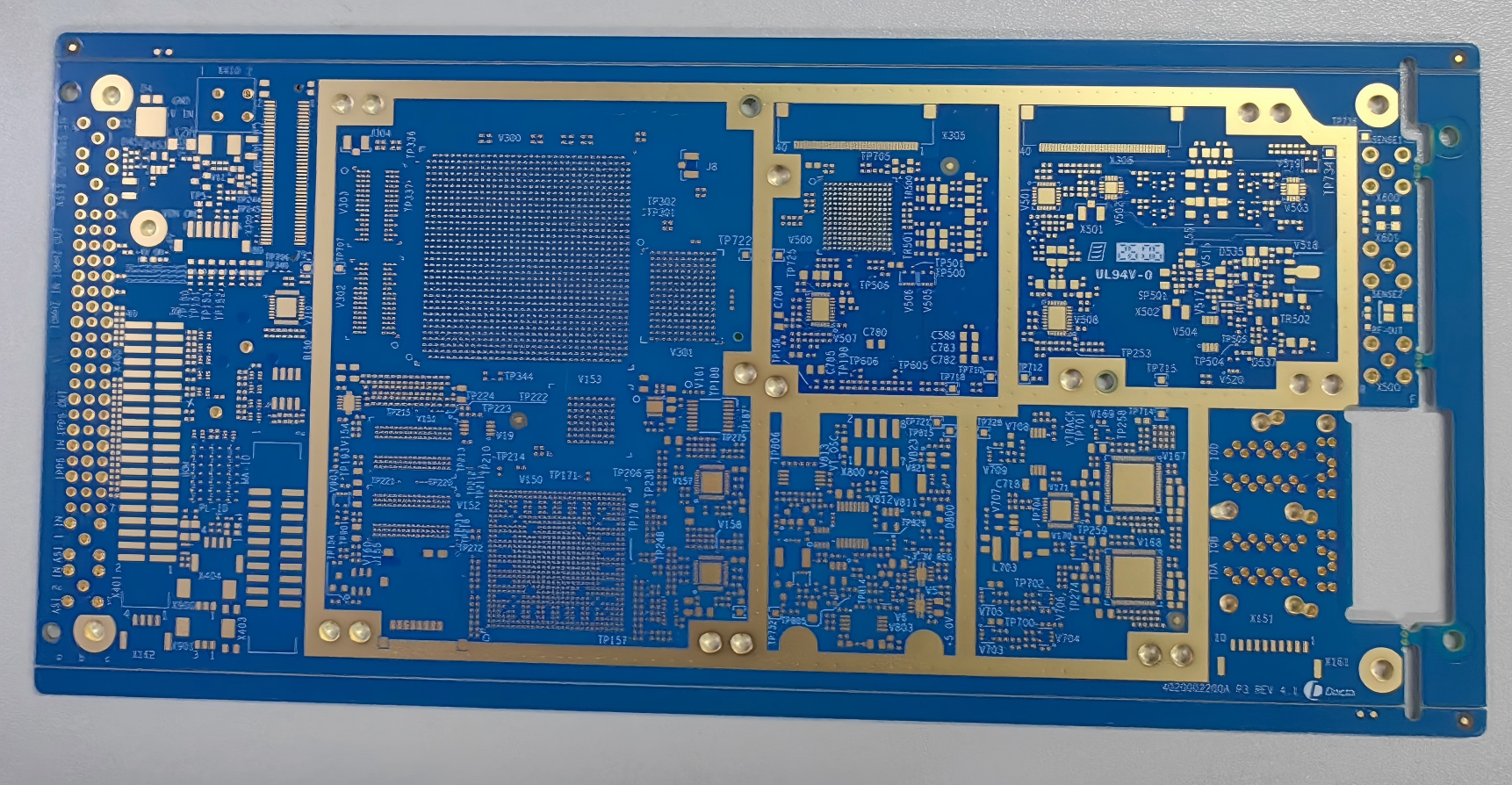

首页/新闻动态/一次讲透存储器 PCB 设计:SRAM/DDR/Flash 核心要点

一次讲透存储器 PCB 设计:SRAM/DDR/Flash 核心要点

这份PCB Layout 存储器专题总结非常硬核,直接对应稳定性、速率、良率三大核心,百能云板帮你整理成更清晰、可直接收藏投板核对的版本,结构更紧凑、要点更突出,工程师一看就能用。

PCB Layout:存储器设计核心要点

(SRAM / DDR1~5 / EEPROM / Flash 全汇总)

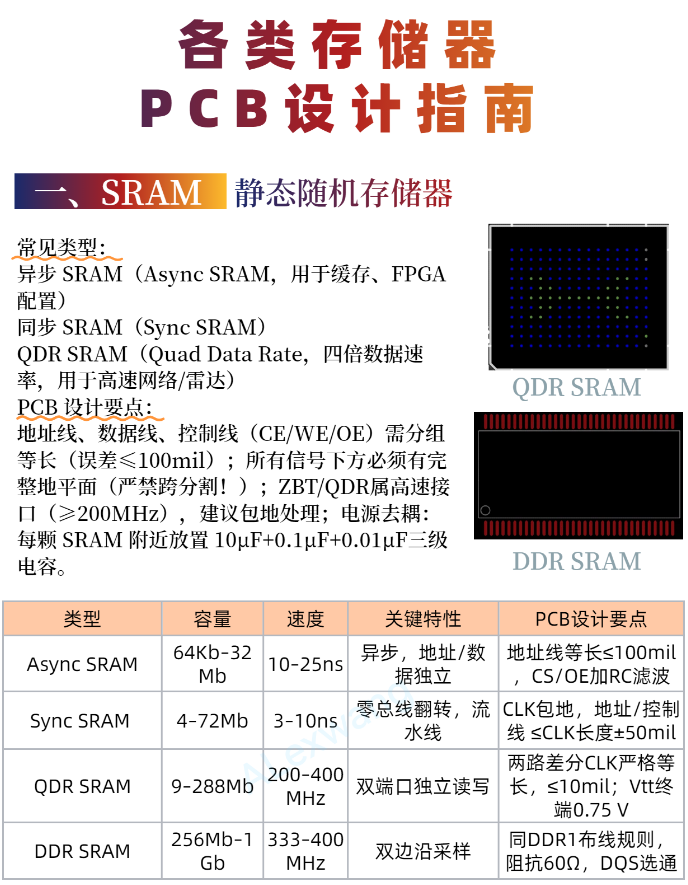

一、SRAM —— 快但怕干扰

类型:异步 SRAM(ZBT)、同步 SRAM、QDR SRAM(高速网络 / 雷达)

Layout 要点:地址 / 数据 / 控制分组等长

CE/WE/OE/ 地址 / 数据分组等长,误差 ≤100mil

完整地平面,严禁跨分割:所有信号下方必须有连续 GND

高速 SRAM 建议包地:ZBT/QDR ≥200MHz,信号两侧包地减少串扰

三级去耦:每颗芯片就近放置:10μF + 0.1μF + 0.01μF

典型风险:走线不等长 → 采样窗口偏移 → 读写异常 / 系统死机

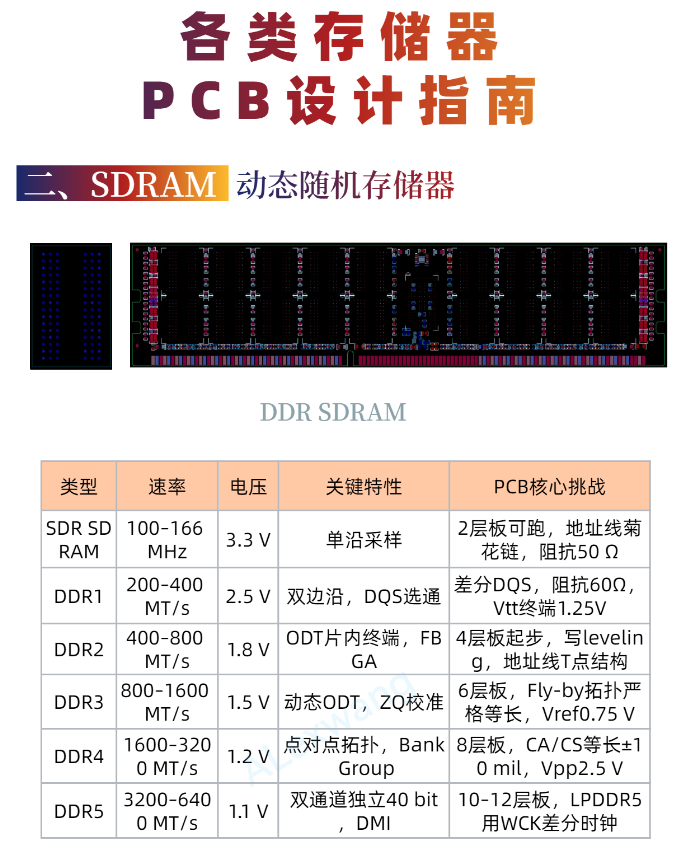

二、DRAM(DDR1~DDR5)—— 高速时序最严苛

通用黄金规则(DDR3~DDR5 通用)

命令 / 地址 / 控制:Fly‑by 拓扑

CLK/CKE/CS/RAS/CAS 菊花链,禁止 T 型分支

DDR3 端接 VTT 电阻;DDR4/DDR5 用 ODT 片内终结

DQ/DQS 严格点对点

一组 DQS 对应 8/16bit DQ,不许分支

组内等长要求:

DDR3:≤50mil

DDR4:≤20mil

DDR5:≤10mil

差分时钟 CLK±

阻抗 100Ω 差分对

长度误差 ≤10mil

远离 DQ 与电源,间距 ≥20mil

电源分区清晰

VDD / VDDQ / VREF 平面严格分割

颗粒引脚旁密集 0402 去耦电容

VREF 建议专用低噪声 LDO

参考平面要求

信号层紧邻完整 GND

DDR 区域下方禁止跨分割、禁止走高频 / 大电流

典型风险

Fly‑by 未终结 → 反射严重

DQ 不等长 → 眼图闭合、读写错误

VREF 噪声 → 误码率飙升、跑不到标称频率

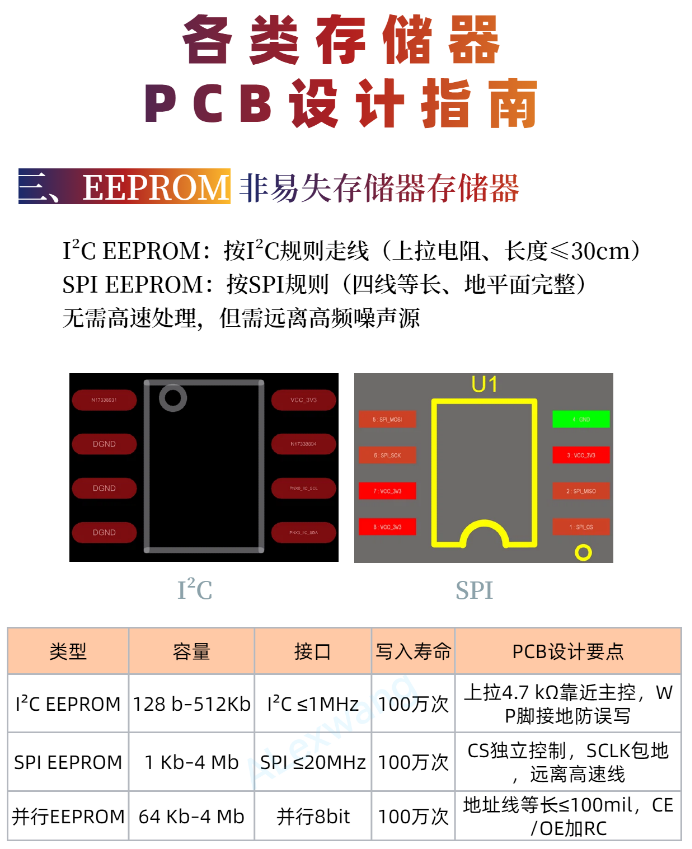

三、EEPROM —— 低速但求稳定

I²C EEPROM

遵循 I²C 规范,SDA/SCL 加合适上拉

走线长度一般 ≤30cm

远离时钟、电源噪声

SPI EEPROM

CS/CLK/DIO/DO 四线尽量等长

下方保持完整地平面

无需阻抗控制,但避免靠近干扰源

四、Flash 类 —— 并行 / 高速接口差异巨大

1. NOR Flash

并行 NOR

地址 / 数据 / 控制分组等长 ≤100mil

OE/WE/CE 同步走线

完整地平面

Serial NOR(SPI / QSPI)

QSPI IO0~3 等长 ≤50mil

CLK 包地处理

频率>50MHz 建议做阻抗控制

风险

并行 Flash 不等长 → 地址错乱、读 ID 失败

2. NAND Flash

并行 NAND

时序比 NOR 更敏感,等长要求更严

ONFI / Toggle DDR NAND

差分 DQS 类似 DDR 架构

DQ + DQS 组内等长 ≤20mil

全程完整地参考,禁止跨分割

3. eMMC / UFS

eMMC(HS200 / HS400)

8bit 数据 + 时钟等长 ≤50mil

CLK 包地,远离射频与开关电源

UFS

高速 MIPI 差分对,阻抗 100Ω

Layout 标准接近 MIPI CSI/DSI

风险

eMMC 不等长 → HS200 降频到 HS52,速率大幅缩水

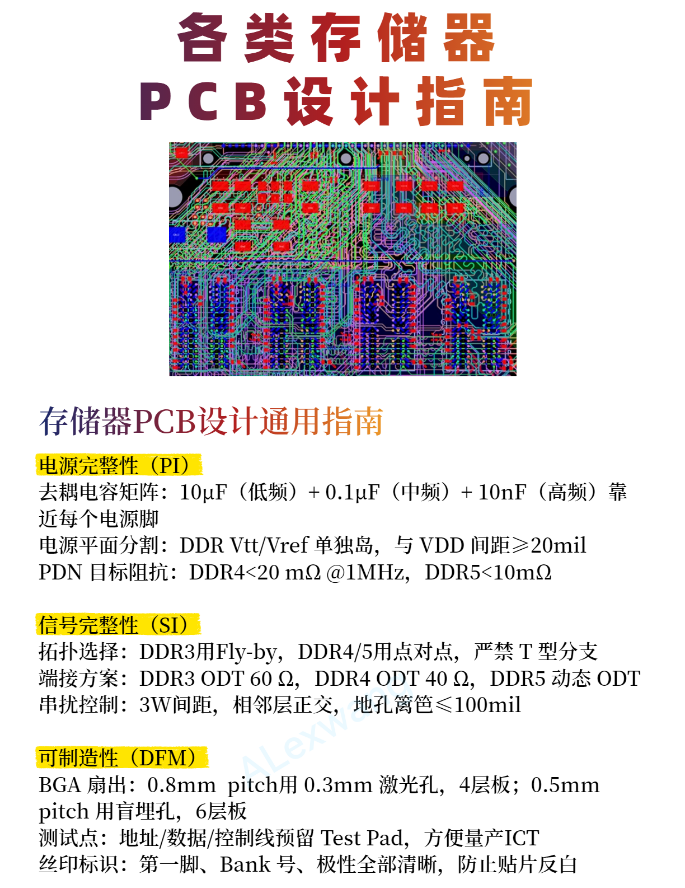

SRAM:分组等长 ≤100mil + 完整地 + 三级去耦

DDR:Fly‑by 命令 + DQ/DQS 严格等长 + 差分时钟 + 电源分割 + 无跨分割

EEPROM:I²C 上拉 / SPI 等长 + 远离噪声

NOR Flash:并行等长,QSPI 等长 + 包地

NAND/eMMC:类 DDR 时序,DQS / 数据等长,地平面完整

热门新闻

方寸铸硬核,精工造非凡|百能云板12层3阶HDI板,助力工业智能进阶

AI高功耗倒逼材料迭代:陶瓷基板开启PCB替代与国产替代新周期