射频PCB电路板设计与优化指南

射频电路已广泛应用于各类电子产品,尤其在医疗、工业控制与通信领域。那么,什么是射频电路板?通常,射频频率覆盖 300 kHz 至 300 GHz,其中超过 300 kHz 即可视为射频,而 300 MHz 以上常被归入微波范畴。与常见的数字电路、模拟电路相比,射频与微波电路在设计上存在显著差异。本质上,射频信号属于极高频率的模拟信号,其电压和电流可在任意时刻连续变化,不同于数字信号的离散电平。此外,射频信号带宽可窄可宽,并借助高频载波进行传输。因此,射频电路在PCB设计上面临着与高速数字电路不同的挑战。

射频电路的设计挑战

PCB 设计工程师在处理射频电路时,主要面临以下四大挑战:

对噪声敏感

射频电路极易受噪声影响,易引发振铃(ringing)与反射现象,必须谨慎处理。

阻抗匹配要求严苛

阻抗匹配是射频设计的关键。频率越高,允许的误差范围越小。当从发射端到接收端的走线总长度超过信号波长 1/16(即临界长度)时,就必须对该走线进行阻抗控制。例如,对于 1 GHz 信号,若走线长度大于约 375 mil,则需实施阻抗控制。

回波损耗需最小化

在微波频段,回波信号需经由电感最小的路径返回。若 PCB 布局不当,回波信号可能窜入电源平面、其他层或相邻线路,导致阻抗失控,增加损耗。

串扰问题突出

串扰随着信号边沿速率提高而加剧,主线路的耦合能量会叠加至相邻信号线上。随着电路板密度提升,串扰问题往往更加显著。

RF PCB 设计解决方案

噪声控制

可采用适当的端接(termination)来抑制反射与振铃,同时借助完整、连续的地平面为回流提供低阻抗路径。

阻抗匹配

在典型射频系统中,通常需保持特征阻抗为50Ω,即从发射端、传输线到接收端均应实现50Ω阻抗匹配,以确保信号高效传输。

回波损耗优化

在信号走线下方保持完整且连续的地平面,可为回波提供稳定路径。这不仅能减小接地回路电流,还可降低射频能量泄漏至其他元件的风险。

串扰抑制

在高速或敏感信号走线周围预留充足间距;

进出射频模块的引线应尽量缩短,并远离其他高速信号;

避免长距离平行走线,减小平行段长度;

可考虑采用共面波导(coplanar waveguide)结构,或减少走线与参考平面间的介质厚度;

在相邻信号线之间插入接地屏蔽线或地平面,可有效降低串扰(通常可达 50% 以上)。

损耗控制

除了上述设计因素,还需关注以下几类信号损耗:

趋肤效应损耗:随着频率升高,电流趋于导体表面流动,导致有效电阻增加,引起损耗。这在射频信号线上尤为明显。

介质损耗:高频信号通过介质材料时,部分电磁能量因介质极化弛豫而转化为热能。FR4 等常规材料的损耗因子(Df)较大,会引入显著的插入损耗。

对于高频及微波电路,建议选用低损耗板材,如聚四氟乙烯(PTFE)基材,其损耗因子可低至 0.001(FR4 一般为 0.02 左右),能大幅降低介质损耗。

层压板选型考虑

设计射频 PCB 时,层压板的以下特性对性能影响重大:

损耗因子(Df):FR4 等常规板材的损耗因子较高,会导致较大的插入损耗,且损耗随频率上升而增加。

介电常数(Dk)及其稳定性:FR4 的 Dk 值可能随频率、温度及批次波动达 10%,影响阻抗一致性。专用高频板材(如 Rogers、Nelco 等)具有更稳定的 Dk 特性。

Dk 值与电路尺寸:在微波频段,较高 Dk 值的板材有助于缩小电路尺寸,但需权衡其与带宽、损耗之间的关系。

射频电路设计实用技巧

为提升射频 PCB 的抗干扰能力与可靠性,可采用以下布局布线技巧:

将内层用作完整的电源/地平面,实现屏蔽并减少杂散电感。

尽量缩短射频信号走线,减少不必要的交叉与耦合。

走线转角建议采用 45° 或圆弧转角,以降低阻抗突变与辐射。

布线宜短不宜长,过孔宜少不宜多,以减小引入的寄生参数。

相邻信号层布线方向宜相互垂直(如一层水平、相邻层垂直),减少层间耦合。

在空余区域适当增加接地铜箔,并多打接地过孔,构建完整屏蔽。

对关键射频线路或干扰源可局部加装屏蔽罩,以隔离干扰。

信号走线应避免形成大环路,推荐使用菊链式(daisy-chain)布局。

在集成电路电源引脚附近合理布置去耦电容,并尽量缩短其接地路径。

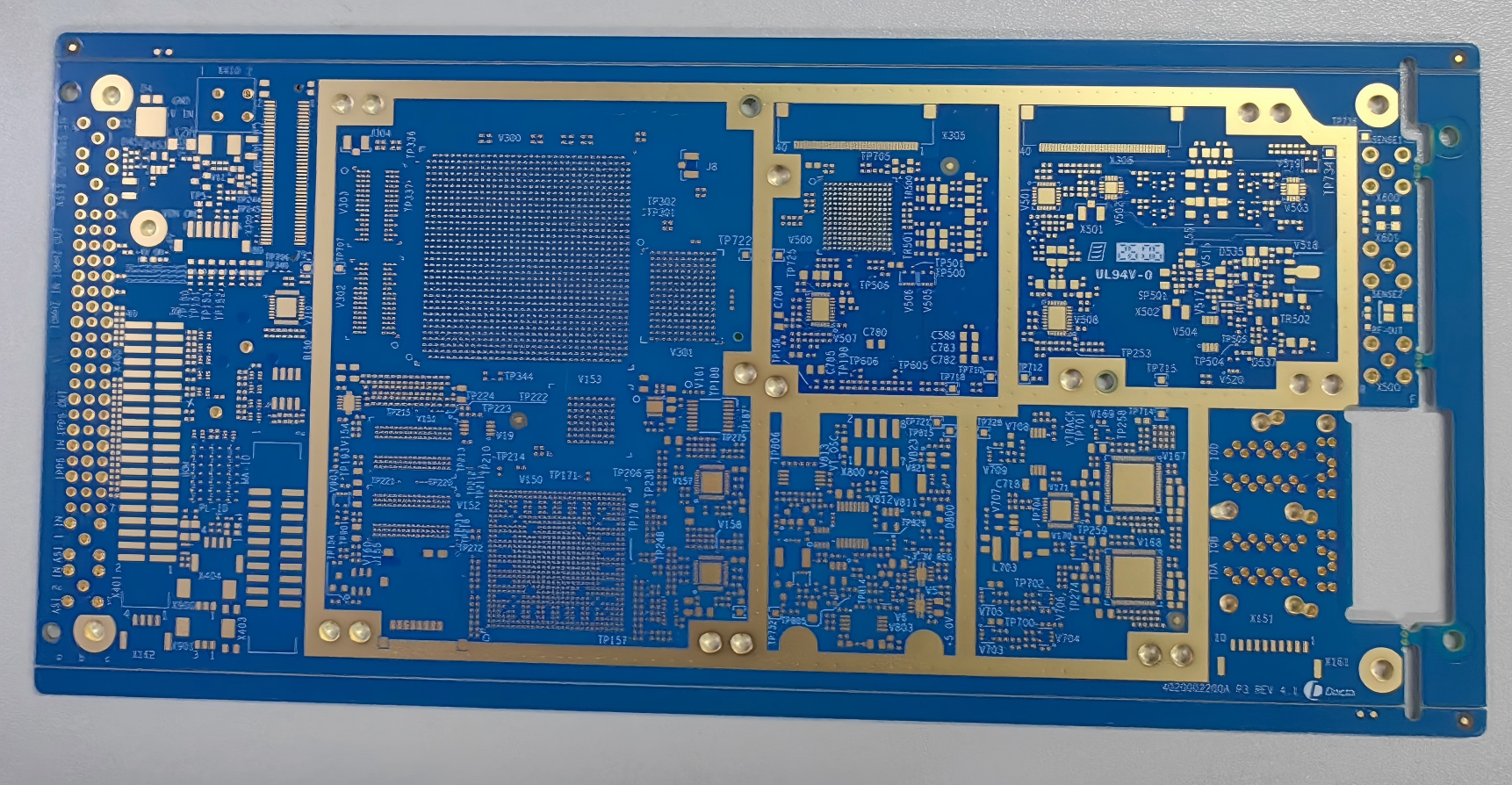

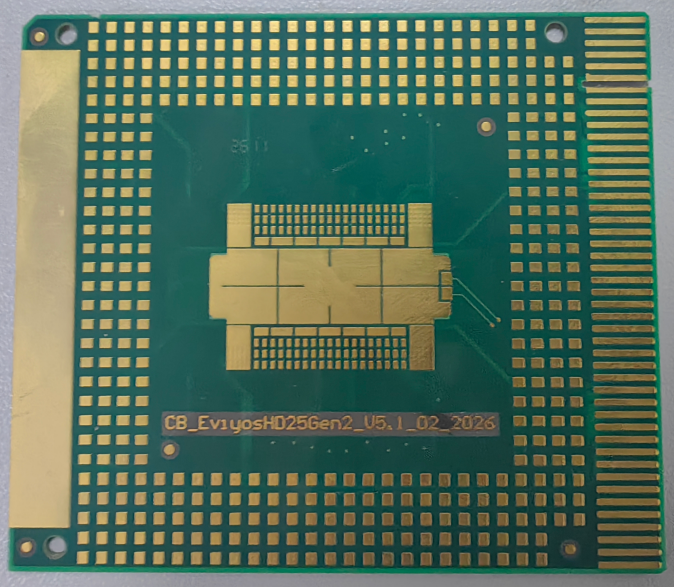

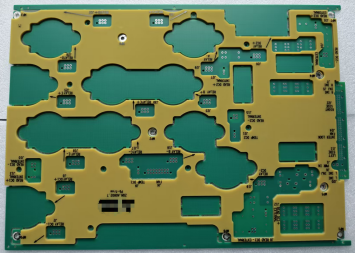

百能云板射频电路板PCB部分产品展示