首页/新闻动态/封装载板制造特殊工艺—无芯工艺与嵌入式线路工艺技术解析

封装载板制造特殊工艺—无芯工艺与嵌入式线路工艺技术解析

在IC载板制造领域,减成法(Tenting)、改良型半加成法(mSAP)与半加成法(SAP)构成了三大主流工艺路线。与此同时,无芯工艺(Coreless)、嵌入式线路工艺(ETS,即Embedded Trace Substrate / Embedded Pattern Process)以及无芯铜柱法(Via Post Coreless)等特种工艺正逐步成为高端封装领域的关键技术补充。这些工艺凭借其在结构设计、布线密度、电性能及薄型化等方面的独特优势,精准满足了AI算力、低轨卫星、智能座舱等前沿应用对封装载板的严苛要求,也成为当前IC载板国产化进程中亟需突破的技术高地。本文聚焦无芯工艺(Coreless)及其衍生技术——嵌入式线路工艺(ETS),结合最新技术进展,系统阐述二者的工艺原理、核心优势及适用场景。

一、无芯载板工艺(Coreless Substrate)

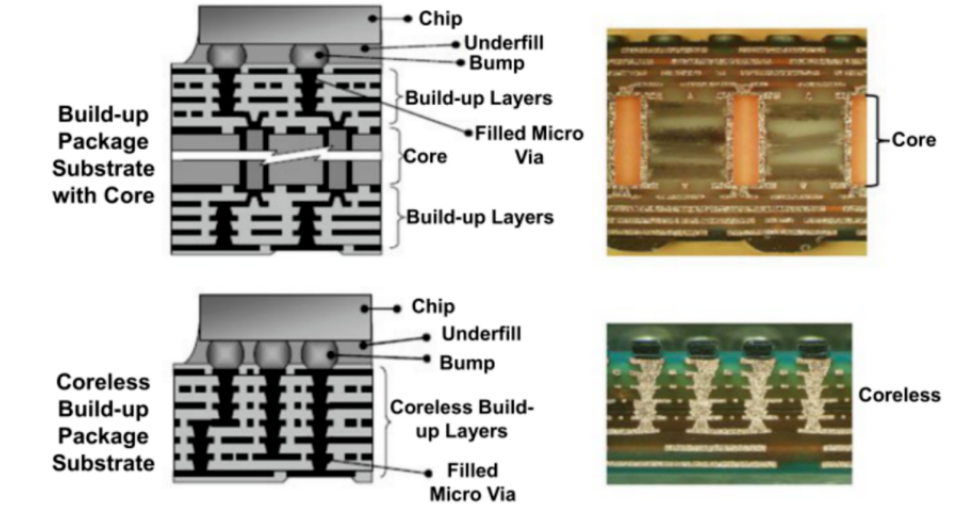

无芯载板由富士通公司于2006年率先提出,其全称为无芯封装载板(Coreless Substrate)。该技术摒弃了传统有机载板中的刚性芯板(Core),完全由高密度积层(Build-up layer)堆叠而成,旨在实现封装载板的极致轻薄化与小型化,满足高端芯片对尺寸缩减、高频信号低损耗的严苛需求。

与传统含芯有机载板相比,Coreless载板最本质的区别在于不含刚性芯层,所有导电层均为积层结构,无需刚性芯板提供机械支撑。其突出特性包括:超薄厚度、低介电常数(Low Dk)、低损耗因子(Low Df),从而在高频高速传输场景下具备显著优势。Coreless载板已广泛应用于高端逻辑芯片(AP)、存储芯片(Memory)、射频芯片(RF)、微机电系统(MEMS)等领域。目前,国内部分企业已实现Coreless载板的量产,并成功进入知名芯片设计企业的供应链体系。

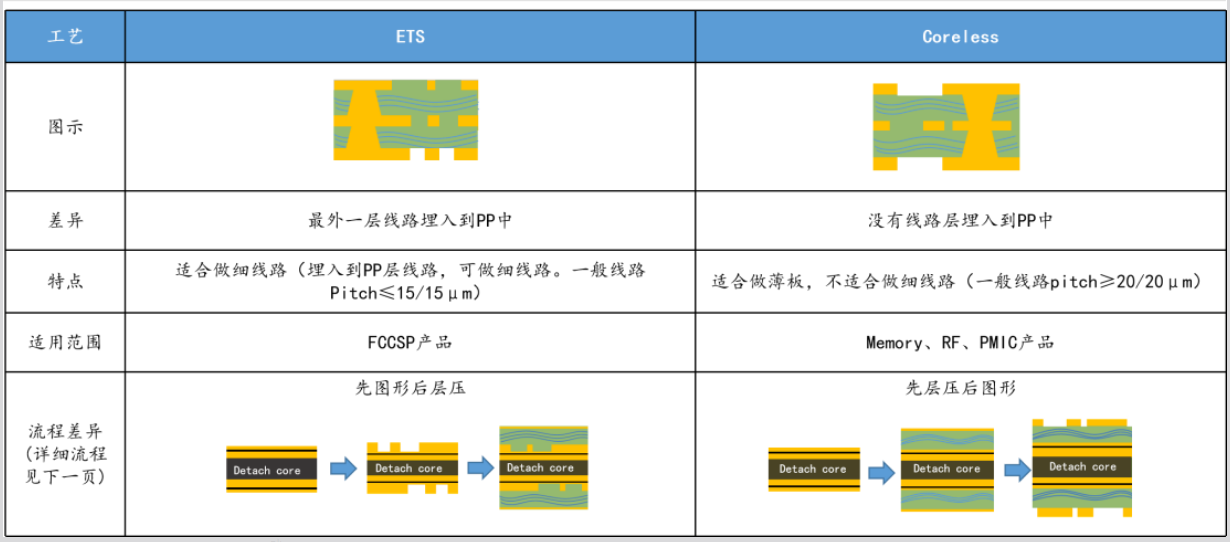

二、嵌入式线路工艺(ETS / EPP)

ETS工艺又称埋线路基板技术,其核心特征在于线路图形与半固化片(PP)表面平齐,故名“平齐基板”。该技术是在Coreless无芯架构基础上进一步优化衍生而来的先进载板制造工艺,被视为突破高端载板技术壁垒、抢占智算时代封装制高点的核心技术之一。

工艺原理:ETS工艺利用可剥离载体(Detach Core)实现线路的嵌入式成型。具体流程为:首先在可剥离的Detach Core表面通过图形电镀或其它方式精准制作线路图形;随后通过层压工艺将半固化片(PP)与载体上的线路紧密贴合,使线路完全嵌入PP介质层内部;完成压合及分板后,通过蚀刻工艺去除载体底铜,最终形成嵌入介质层内的导电图形。该流程有效保障了线路的精细度与表面平整度。

与mSAP工艺的对比优势:

更优的细间距能力:ETS线路完全嵌入PP介质内部,无需经历侧向蚀刻,避免了传统半加成法中因侧蚀造成的线宽损失,可实现更小的线宽/线距(L/S)。

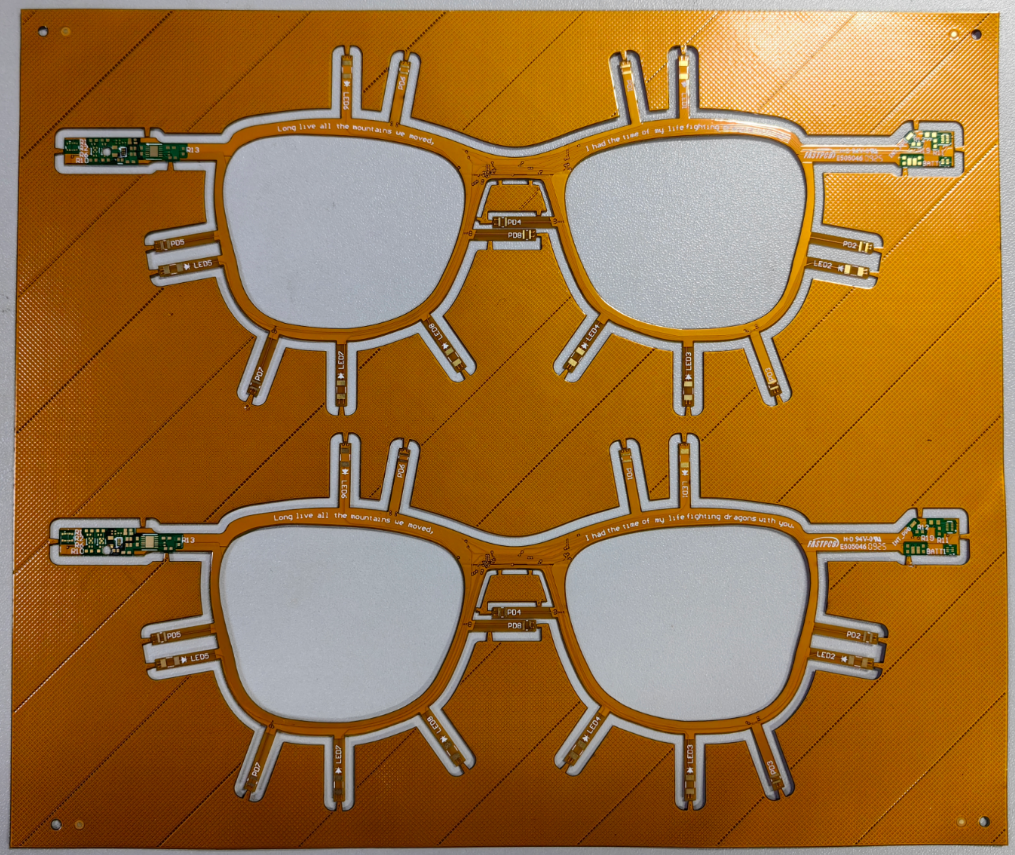

突出的薄型化能力:依托Detach Core的稳定支撑,ETS工艺能精确控制整体厚度,轻松满足超薄封装需求,尤其适用于AI加速卡、高阶系统级封装等尖端产品。

在ETS结构中,电路图案内嵌于绝缘介质层内部,结合其无芯结构特征,使得微细电路的实现无需额外成本,并显著降低层数缩减的难度——例如可便捷地将4层设计优化为3层。由于蚀刻工艺不依赖于图案宽度,线路宽度可得到精确控制。因此,ETS成为大规模生产L/S < 12μm精细线路的优选方法。截至2026年,业内已知ETS技术可实现的最小L/S为5/5μm;国内企业已稳定量产15/15μm线宽线距,部分领先企业可挑战12/12μm。

目前,ETS技术主要用于2层、3层或4层基板中单一电路层的构建,并可进一步扩展为垂直堆叠多层ETS图案,以满足更高密度的集成需求。需要特别指出的是,ETS线路与顺序积层半加成法(SAP)线路在形态上存在本质区别:ETS线路完全内嵌于覆铜板(CCL)的介电层内部,而SAP线路则位于介电层之上。然而,二者线路截面均呈矩形,有利于信号传输的稳定性,适应高频高速封装场景。

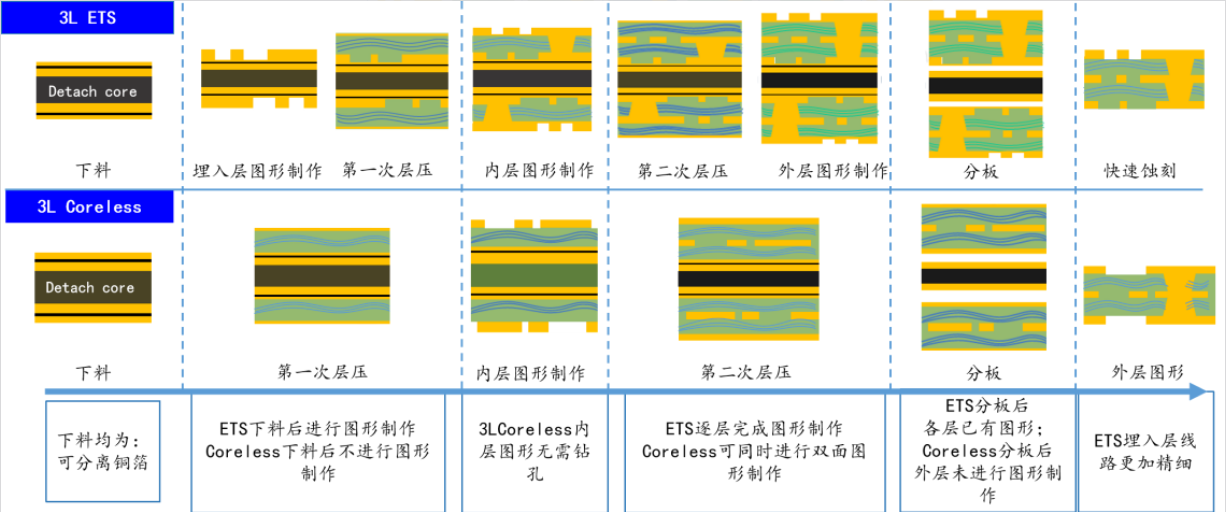

三、ETS工艺的两种实现方法

1. 图形电镀法(Pattern Plating approach)

该方法以可剥离载体(Detach Core)为核心支撑,用于构建精细线路。通常使用厚度小于25μm的薄干膜实现精细图形,线路铜厚控制在10~15μm。随后通过压合、分板将图案转移至半固化片中,分板后蚀刻去除底铜。导通孔(盲孔)一般从埋线层的另一侧采用激光烧蚀形成。由于PP材料富含树脂,能够有效保护线路铜,避免其直接接触玻璃纤维,从而防止导电阳极丝(CAF)缺陷,显著提升产品可靠性。该方法目前是业界应用最广泛的技术路线,国内如广芯基板、兴森快捷、越亚半导体、安捷利美维、红板科技等企业均已实现量产。

2. 激光刻槽法(Laser Trenching approach)

该方法采用普通芯板(Core)作为起始材料。首先在板材一面生成图形,另一面通过激光烧蚀精确加工出具有精细间距的高密度电路沟槽,同时烧蚀出盲孔。随后采用特殊电镀工艺对ETS面进行全板电镀,该工艺优先在沟槽和过孔内沉积金属,最大限度地减少后续闪蚀需要去除的冗余铜层,从而降低制程损耗。需要注意的是,激光烧蚀的图案化速率相对较慢,整体产能低于激光直接成像(LDI)工艺;此外,任何烧蚀不均匀(如深度过大或过浅)都可能在最终产品中引入潜在缺陷。因此,该方法目前的应用范围不及图形电镀法。